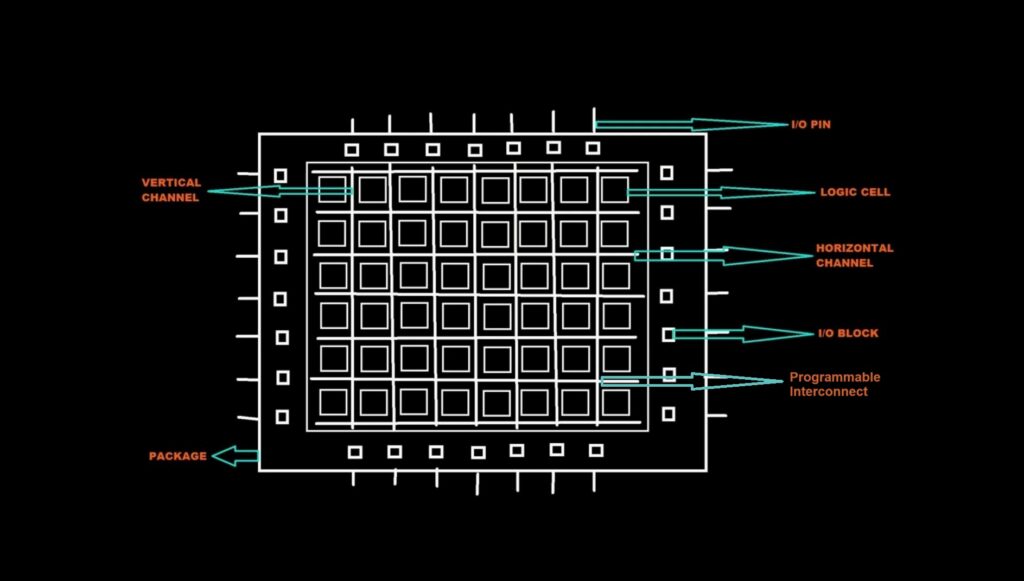

Field Programmable Gate Array Pdf Field Programmable Gate Array The iobs provide a programmable interface between the internal; array of logic blocks (clbs) and the device’s external package pins. clbs perform user specified logic functions, and the interconnect resources carry signals among the blocks. New york 2012 7 2.1 introduction to fpgas field programmable gate arrays (fpgas) are pre fabricated silicon devices that can be electrically programmed in the field to become alm.

Field Programmable Gate Array Fpga Architecture Fpga Building blocks of modern fpga architectures a programmable array of logic blocks (lut, ff), interconnects, i os, and dedicated blocks (bram, dsp) ⋮ ⋮ dsp. Field programmable gate arrays (fpgas) represent a versatile and powerful class of integrated circuits that offer a unique blend of flexibility and performance. unlike traditional application specific integrated circuits (asics), fpgas are programmable at the hardware level after manufacturing. Pdf | a survey of field programmable gate array (fpga) architectures and the programming technologies used to customize them is presented. A pre fabricated off the shelf fpga can be used to implement a complete system in a matter of weeks, and also enables continuous hardware upgrades to support new features or fix bugs by simply loading a new bitstream after deployment in field, thus the name field programmable.

Field Programmable Gate Array Fpga Architecture Pdf | a survey of field programmable gate array (fpga) architectures and the programming technologies used to customize them is presented. A pre fabricated off the shelf fpga can be used to implement a complete system in a matter of weeks, and also enables continuous hardware upgrades to support new features or fix bugs by simply loading a new bitstream after deployment in field, thus the name field programmable. What is a field programmable gate array ? what is inside an fpga? today: up to >1000 user i o pins input and or output voltages from (1.0), 1.2 3.3 v many io standards single ended: lvttl, lvcmos, differential pairs: lvds,. Itectu comprises the wiring segments and routing switches that interconnect the fpga’s logic cells. each of the user programmable switches in an fpga consumes significant chip area and has appreciable capacitance and resistance, leading to a tradeoff in the design of a good routing architecture. Figure 1: field programmable gate array chip classified as simple programmable logic devices (splds). these splds were incorporated onto a single chip and interconnects were provided to connect the spld blocks through programming. these were called complex plds and were first initiated by altera. Xilinx: basic clb architecture look up table (lut) implements truth table memory elements: flip flop latch some fpgas luts can also implement small rams carry & control logic implements fast adders subtractors.

Pdf Field Programmable Gate Array Fpga What is a field programmable gate array ? what is inside an fpga? today: up to >1000 user i o pins input and or output voltages from (1.0), 1.2 3.3 v many io standards single ended: lvttl, lvcmos, differential pairs: lvds,. Itectu comprises the wiring segments and routing switches that interconnect the fpga’s logic cells. each of the user programmable switches in an fpga consumes significant chip area and has appreciable capacitance and resistance, leading to a tradeoff in the design of a good routing architecture. Figure 1: field programmable gate array chip classified as simple programmable logic devices (splds). these splds were incorporated onto a single chip and interconnects were provided to connect the spld blocks through programming. these were called complex plds and were first initiated by altera. Xilinx: basic clb architecture look up table (lut) implements truth table memory elements: flip flop latch some fpgas luts can also implement small rams carry & control logic implements fast adders subtractors.