Vhdl Fpga Pdf Vhdl Bibliothèque Logicielle Formal verification techniques can help you map a requirement to a test, proving that your vhdl module conforms to the specification. it’s an instrumental tool for verifying healthcare applications or gaining do 254 certification for airborne fpga solutions. Osvvm is an advanced verification methodology that defines a vhdl verification framework, verification utility library, verification component library, scripting api, and co simulation capability that simplifies your fpga or asic verification project from start to finish.

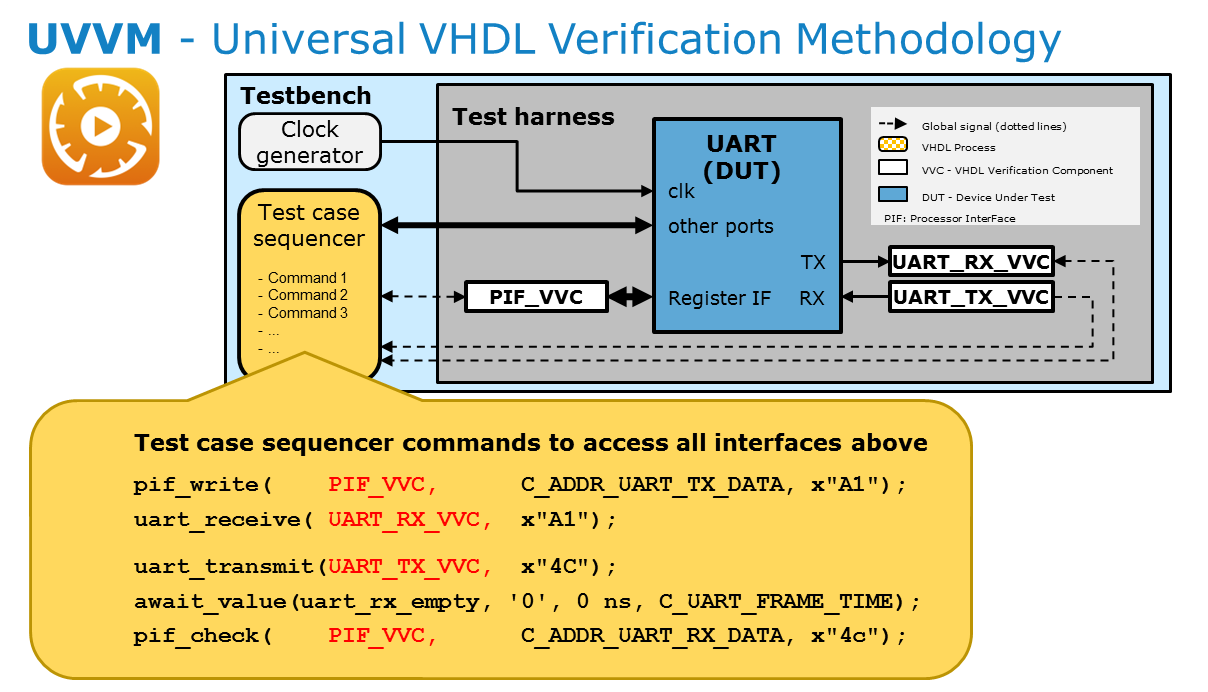

Fpga Vhdl Verification The group will be following the policies of the ieee standards association and cooperate to make uvvm the best possible verification library and methodology for vhdl designers in order to speed up fpga and asic development and improve product quality. In this comprehensive overview, we will explore the fpga verification process, its components, and the significant benefits it offers in ensuring the reliability and functionality of fpga based designs. Uvvm (universal vhdl verification methodology) is a free and open source methodology and library for making very structured vhdl based testbenches. overview, readability, maintainability, extensibility and reuse are all vital for fpga development efficiency and quality. One of the most important aspects when developing fpga is to ensure the modules we have developed are properly tested. depending on the language we use there are several free simulators and frameworks available.

Fpga Verification Poucki Uvvm (universal vhdl verification methodology) is a free and open source methodology and library for making very structured vhdl based testbenches. overview, readability, maintainability, extensibility and reuse are all vital for fpga development efficiency and quality. One of the most important aspects when developing fpga is to ensure the modules we have developed are properly tested. depending on the language we use there are several free simulators and frameworks available. Getting a kick start on your testbench by using available uvvm verification components for axi4 full lite stream, avalon mm, sbi, spi, i2c, uart; and use these as templates for your own. Looking to improve your vhdl fpga verification methodology? osvvm is an ideal solution. it has all the pieces needed for verification. there is no new language to learn. I am investigating the usability of formal verification in fpga designs using vhdl, psl, symbiyosys, and ghdl. i've watched several webinars, read a psl book, and gone through tutorials. Uvvm was made exactly for this and is free and open source and used by 35 40% of all fpga vhdl designers world wide. a new esa (european space agency) project has just been initiated to extend uvvm even further.

Github Uniphos Vhdl Fpga Code Getting a kick start on your testbench by using available uvvm verification components for axi4 full lite stream, avalon mm, sbi, spi, i2c, uart; and use these as templates for your own. Looking to improve your vhdl fpga verification methodology? osvvm is an ideal solution. it has all the pieces needed for verification. there is no new language to learn. I am investigating the usability of formal verification in fpga designs using vhdl, psl, symbiyosys, and ghdl. i've watched several webinars, read a psl book, and gone through tutorials. Uvvm was made exactly for this and is free and open source and used by 35 40% of all fpga vhdl designers world wide. a new esa (european space agency) project has just been initiated to extend uvvm even further.