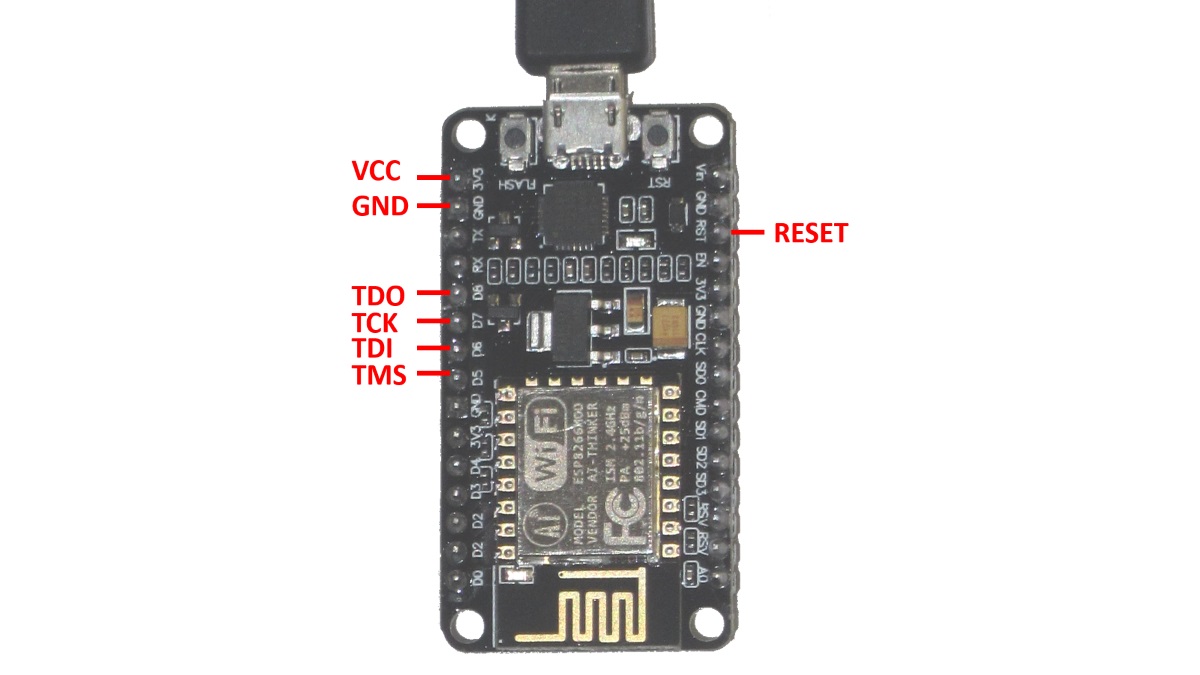

Jtag Debugging The Esp32 With Ft2232 And Openocd Mcu On 48 Off 原文 jtag is the acronym for joint test action group, a name for the group of people that developed the ieee 1149.1 standard. the functionality usually offered by jtag is debug access (through user data registers) and boundary scan (through boundary scan registers) – • debug access is used by debugger tools to access the internals of a chip (like registers, some control bits), while. Jtag (joint test action group) was designed largely for chip and board testing. it is used for boundary scans, checking faults in chips boards in production. debugging and flashing micros was an evolution in its application over time. jtag is in use for multiple microcontroller processor architectures aside from arm. general discussion.

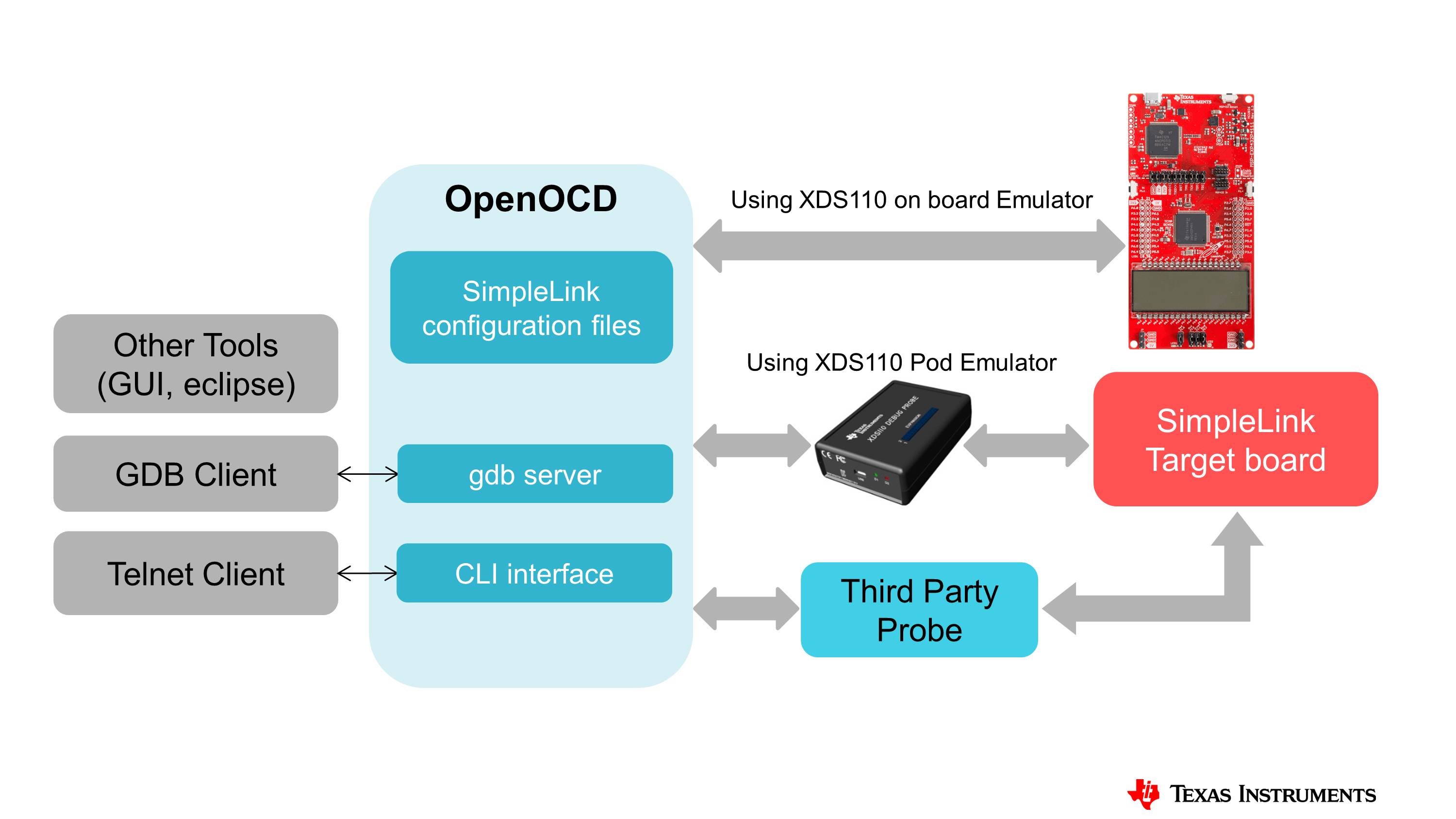

Jtag Debugging The Esp32 With Ft2232 And Openocd Mcu On Additionally, jtag is sometimes mis used as a verb meaning, generically, "to debug test" a thing. a person "jtag'ing something" may actually be using a different protocol that the device's manufacturer has overlapped with the physical jtag pins (i.e. swd). The virtual jtag user guide notes that the virtual jtag intel fpga ip core tcl api requires an intel programming cable.designs that use a custom controller to drive the jtag chain directly must issue thecorrect jtag ir dr transactions to target the virtual jtag intel fpga ip coreinstances. I get the difference between the jtag trst (tap reset) and srst (system reset) signals. if the target chip has these two pins, its wiring to a 20 pin jtag connector is obvious: basically you just connect trst to trst and srst to srst. each of the signals should have a pull up resistor. that's it. however, what if the target chip has no trst pin?. Jtag very generic term, spi like interface used for boundary scan, can also be used for programming debugging mcus (almost every vendor has its own protocol, so cortex m jtag is not the same as avr jtag or blackfin jtag) spy bi wire yet another two wire programming interface, this one is for ti's msp430 mcus is explained here.

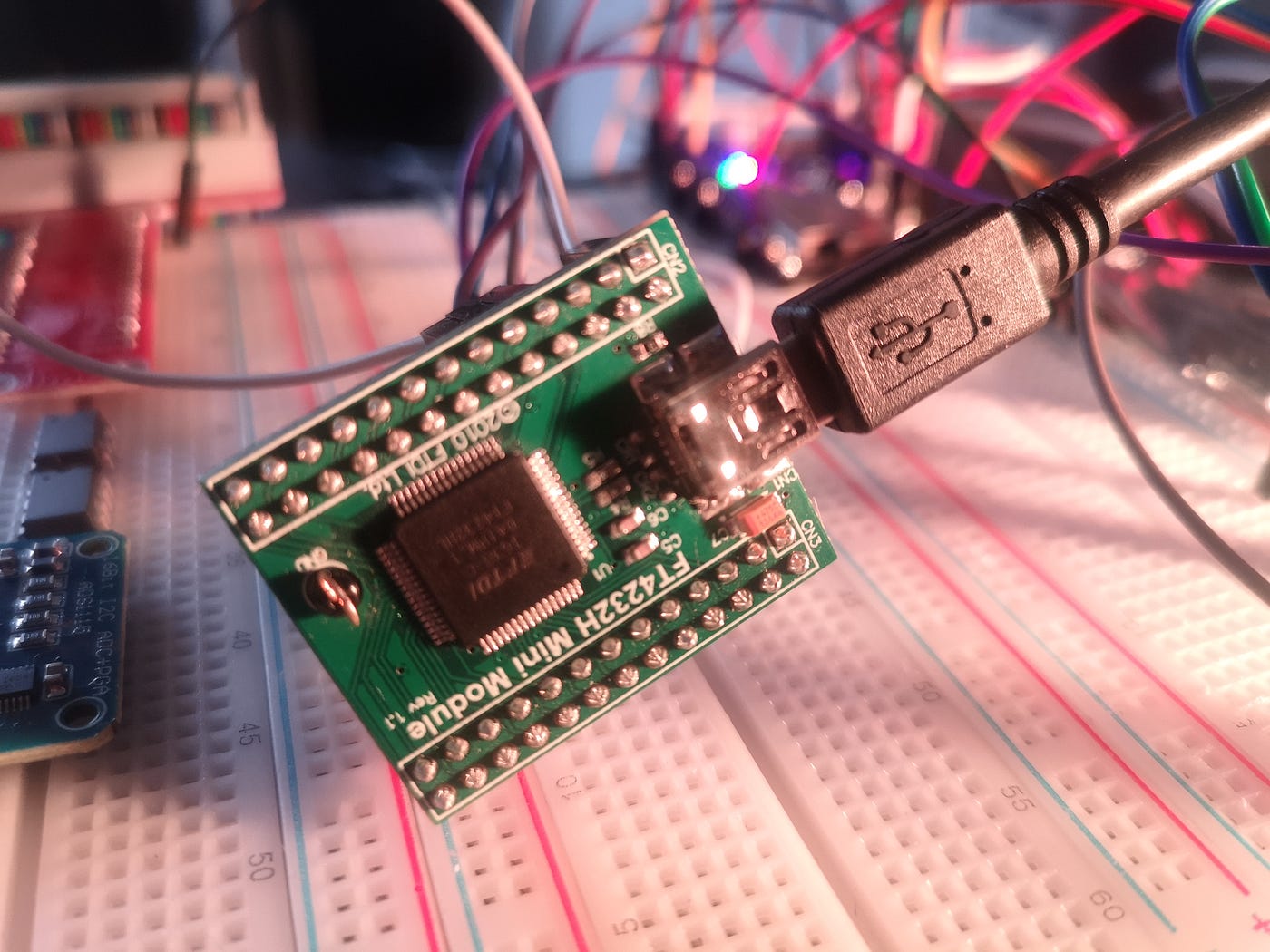

Jtag Debugging The Esp32 With Ft2232 And Openocd Mcu On I get the difference between the jtag trst (tap reset) and srst (system reset) signals. if the target chip has these two pins, its wiring to a 20 pin jtag connector is obvious: basically you just connect trst to trst and srst to srst. each of the signals should have a pull up resistor. that's it. however, what if the target chip has no trst pin?. Jtag very generic term, spi like interface used for boundary scan, can also be used for programming debugging mcus (almost every vendor has its own protocol, so cortex m jtag is not the same as avr jtag or blackfin jtag) spy bi wire yet another two wire programming interface, this one is for ti's msp430 mcus is explained here. I am writing a program for bit banging a jtag interface. as far as i understood the jtag interface, it should act like this: on clock rise, the tdi and tms inputs are sampled, if shift ir or shift. I've noticed, with regards to microcontrollers, there are several way to program them. i am sorta familiar with usb as my arduino's can be programmed via usb. what is a jtag or spi interface?. I'm new with ft4232h. i just make for myself a ft4232h device with 4 channels uart. (custom board for learning and researching) and i want change channel a and b to jtag for debugging stm32 using j. Jtag can support a star topology, but this relies on the individual nodes having control to tri state their tdo drivers (which can then be wire ored). it is possible to switch just the tms inputs to each node, or for the nodes to implement a chip select register within their jtag interface.