Optimizing Fpga Based Accelerator Design For Deep Convolutional Neural As a case study, we implement a cnn accelerator on a vc707 fpga board and compare it to previous approaches. our implementation achieves a peak performance of 61.62 gflops under 100mhz working frequency, which outperform previous approaches significantly. Acceleration platforms convolutional neural network (cnn) has been widely employed for image recognition for its ability to achieve high accuracy. recently, various fpga based accelerators for deep cnn have been proposed.

Optimizing Fpga Based Accelerator Design For Deep Convolutional Neural Among these accelerator designs, fpga and asic based designs can be fully customized to implement the neural network functionality with improved latency, throughput, and energy. Polyhedral based optimization framework can be utilized to execute automatic loop transformation to permute the parallel loop levels to the innermost quantities to prevent loop brought. As a case study, we implement a cnn accelerator on a vc707 fpga board and compare it to previous ap proaches. our implementation achieves a peak performance of 61.62 gflops under 100mhz working. Optimizing fpga based accelerator design for deep convolutional neural networks chen zhang et al louis tw kim presentation.pdf performance analysis of cnn frameworks for gpus.pdf readme.md scalpel customizing dnn pruning to the underlying hardware parallelism,.pdf.

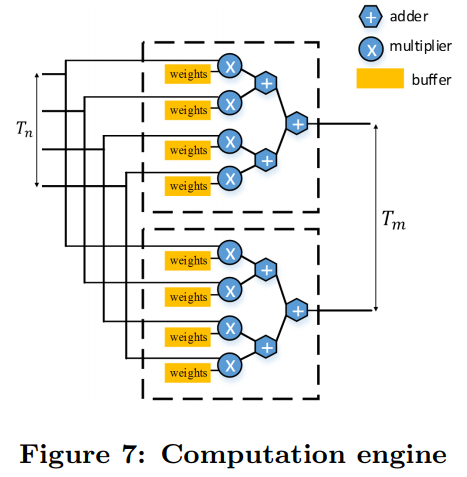

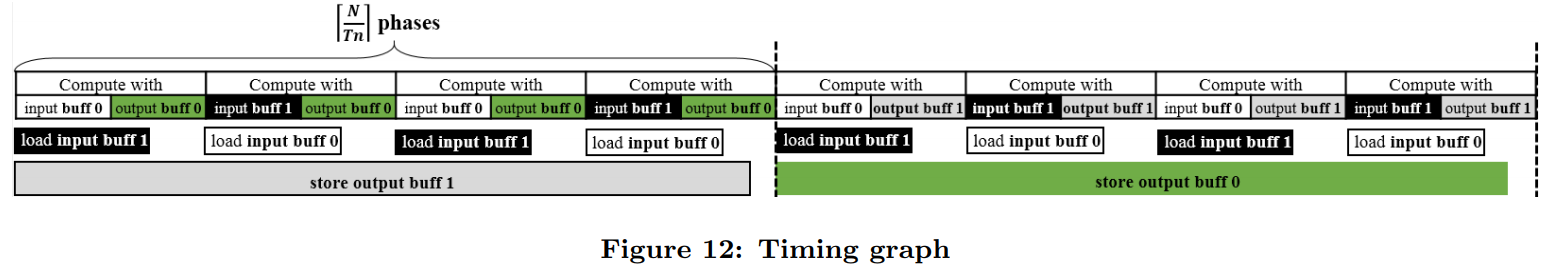

Optimizing Fpga Based Accelerator Design For Deep Optimizing Fpga As a case study, we implement a cnn accelerator on a vc707 fpga board and compare it to previous ap proaches. our implementation achieves a peak performance of 61.62 gflops under 100mhz working. Optimizing fpga based accelerator design for deep convolutional neural networks chen zhang et al louis tw kim presentation.pdf performance analysis of cnn frameworks for gpus.pdf readme.md scalpel customizing dnn pruning to the underlying hardware parallelism,.pdf. Identify all possible solutions in the design space using a roofline model and find the optimal solution for each layer in design space. propose cnn accelerator design with uniform loop unroll factors across different convolutional layers. How to optimize fpga based deep neural network (dnn) accelerator in terms of loop manipulation? and how does roofline model affect to performance in fpga design? why fpga? fpga (field prgrammable gate array) is powerful development platform to design specific purpose of hardware. In this paper, we propose a method to improve accelerator performance by optimizing data management, and improve the computing efficiency and parallelism of accelerators through three optimization strategies. Optimizing fpga based accelerator design for deep convolutional neural network chen zhang1, peng li3, guangyu sun1,2, yijin guan1, bingjun xiao3, jason cong1,2,3.